## Electronics

Jimmy sebastian

### Basic comparator

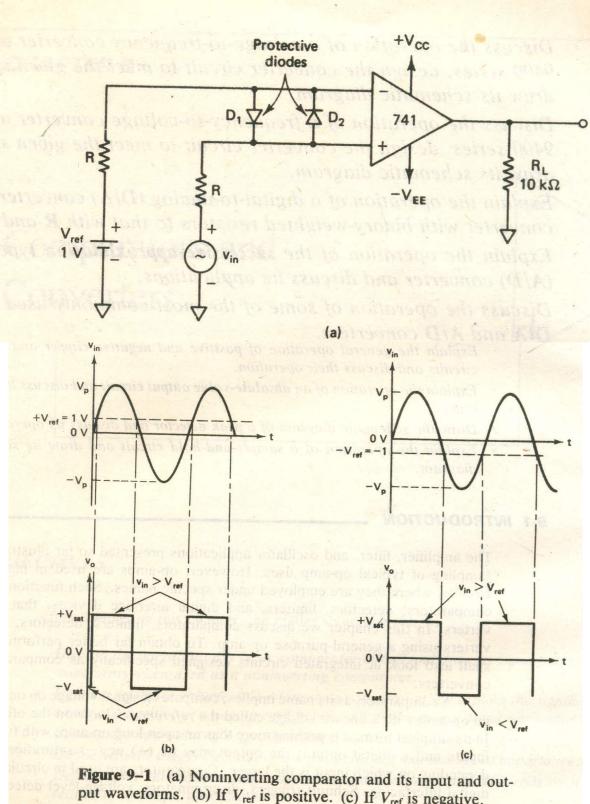

### put waveforms. (b) If $V_{ref}$ is positive. (c) If $V_{ref}$ is negative.

### Noninverting comparator

A fixed reference voltage Vref = 1V is applied at (-) input and a time varying voltage Vin is applied at (+) input. It is also called Noninverting comparator

When vin is less than Vref the output voltage V0 = Vsat (-VEE) and When vin is greater than Vref the output voltage V0 = Vsat (+Vcc)

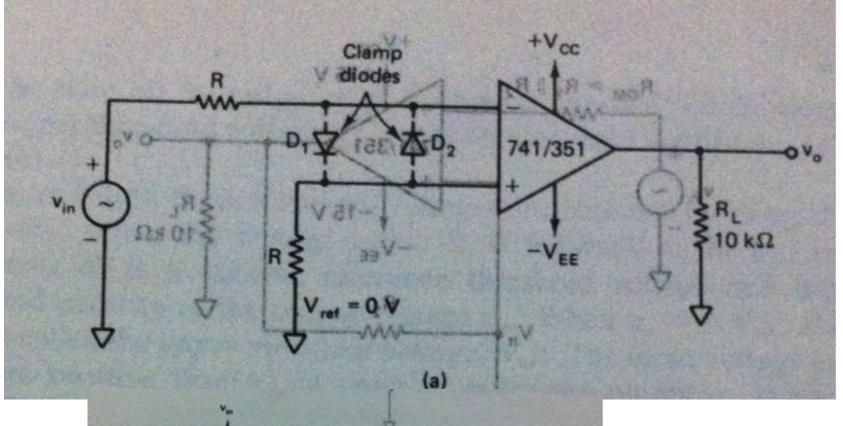

The diodes D1 and D2 are called clamp diodes They protect the opamp from damage due to excessive input voltage Vin. Because of these diodes the input difference voltage is clamped to either 0.7 or -0.7 V.

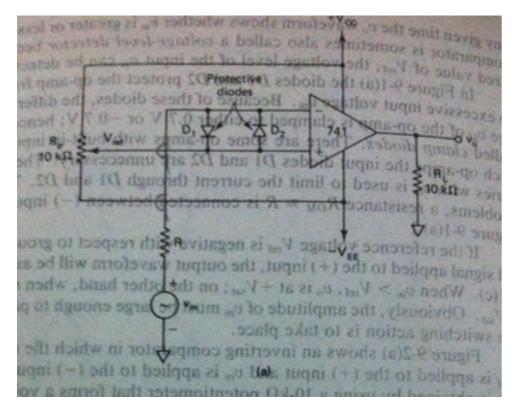

### Inverting comparator

A fixed reference voltage Vref is applied at (+) input and a time varying voltage Vin is applied at (-) input. It is also called inverting comparator

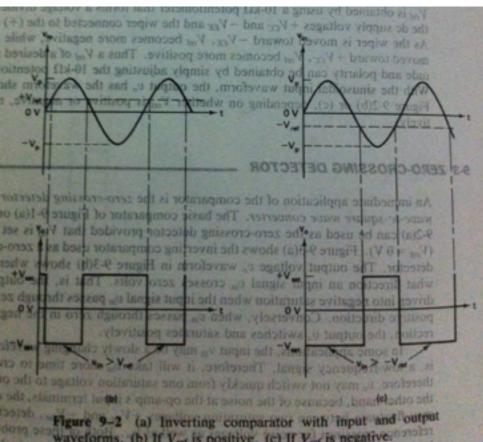

Application of the comparator Zero crossing detector

Figure 9-3 (a) Zero-crossing detector. (b) Its typical input and

output waveforms

The application of the comparator is a zero crossing detector or a sine wave to square wave converter. here Vref is set to 0V

The output V0 is driven to negative saturation when input Vin crosses zero volts in the positive direction

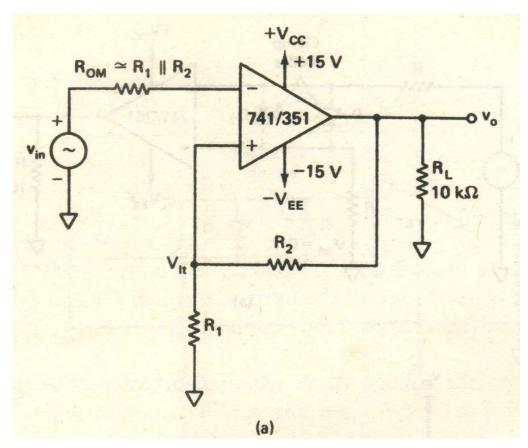

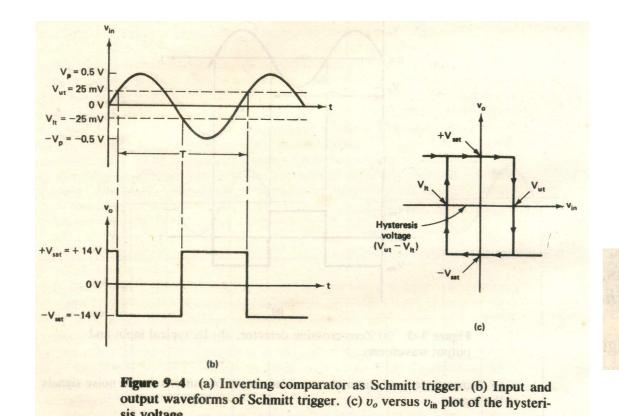

### Schmitt Trigger

The circuit converts an irregular shaped waveform to a square wave or pulse. The input voltage vin triggers the output v0 every time it exceeds certain voltage levels called upper threshold voltage Vut and lower threshold voltage VIt.

$$V_{\rm ut} = \frac{R_1}{R_1 + R_2} \left( + V_{\rm sat} \right)$$

$$V_{\rm lt} = \frac{R_1}{R_1 + R_2} \left( -V_{\rm sat} \right)$$

$$V_{\text{hy}} = V_{\text{ut}} - V_{\text{lt}}$$

$$= \frac{R_1}{R_1 + R_2} [+V_{\text{sat}} - (-V_{\text{at}})]$$

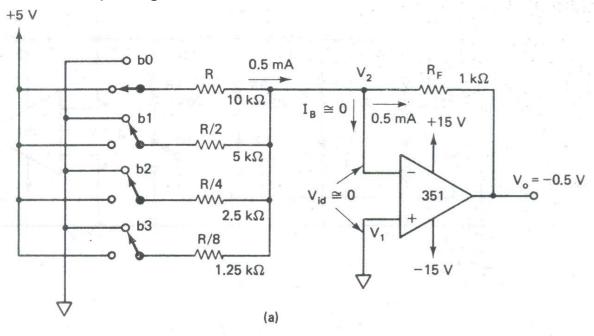

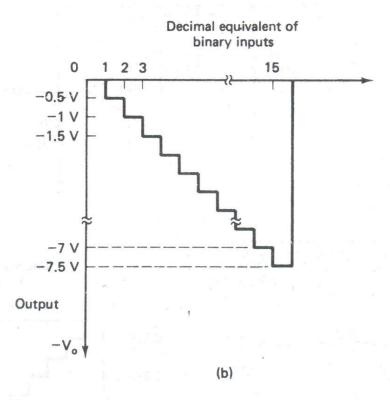

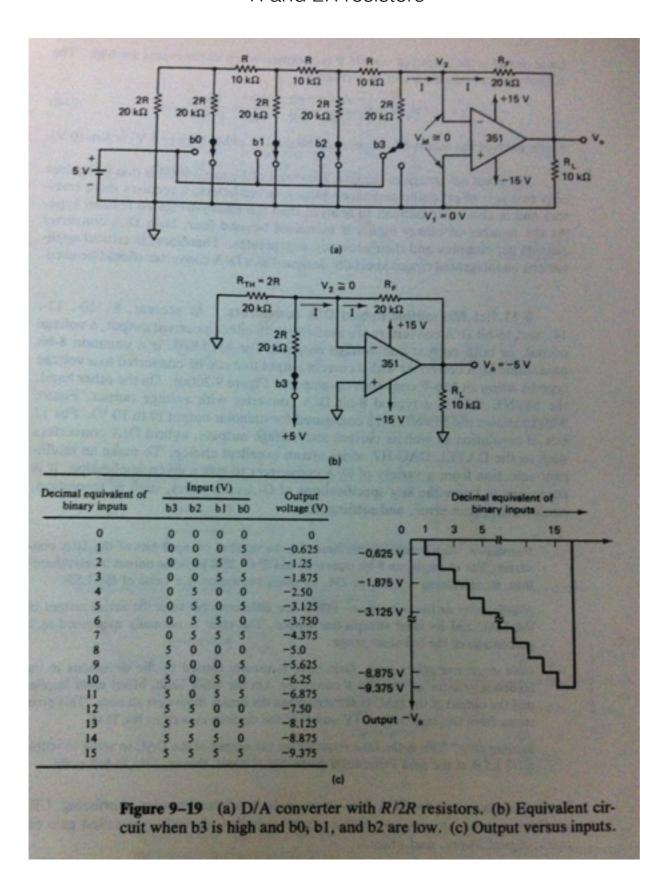

### Digital to Analog converter

#### binary weighted resisters

A D/A converter uses an opamp and either binary weighted resisters or R and 2R resisters.

**SURE 8–18** (a) D/A converter with binary-weighted resistors. (b) Graph of output sus inputs.

#### R and 2R resisters

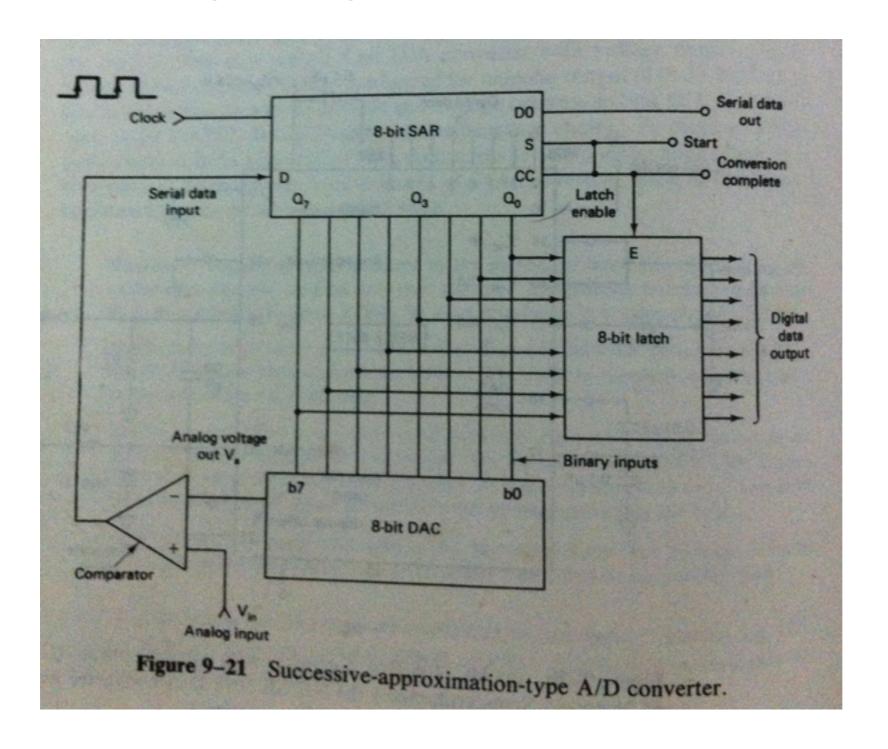

### Analog to digital converter (A/D)

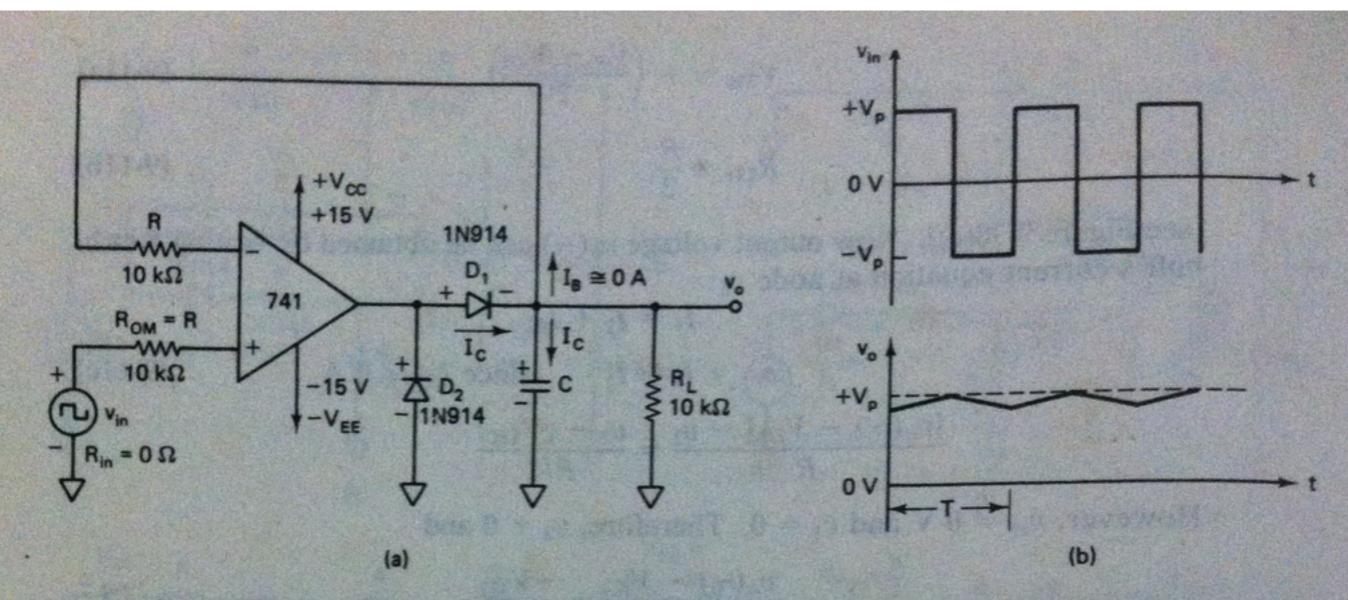

### Peak Detector

Figure 9-31 (a) Peak detector circuit. (b) Its input and output waveforms.

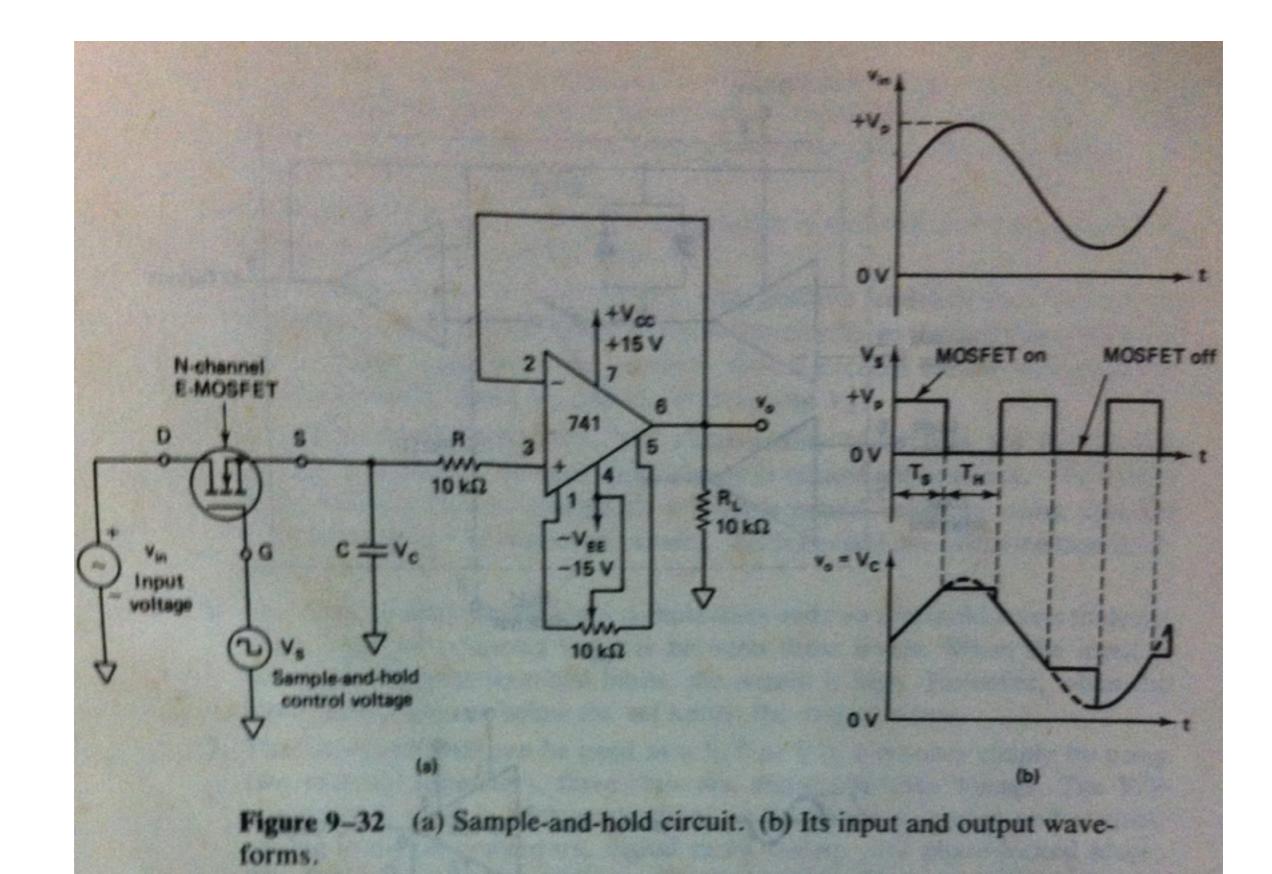

### Sample and hold circuit

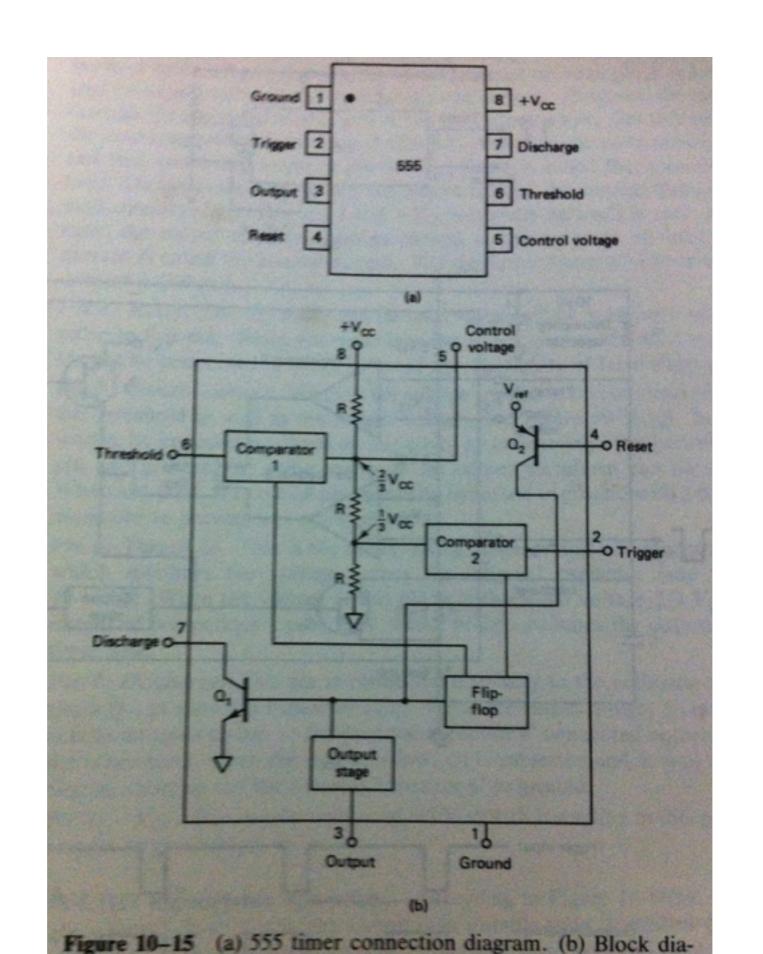

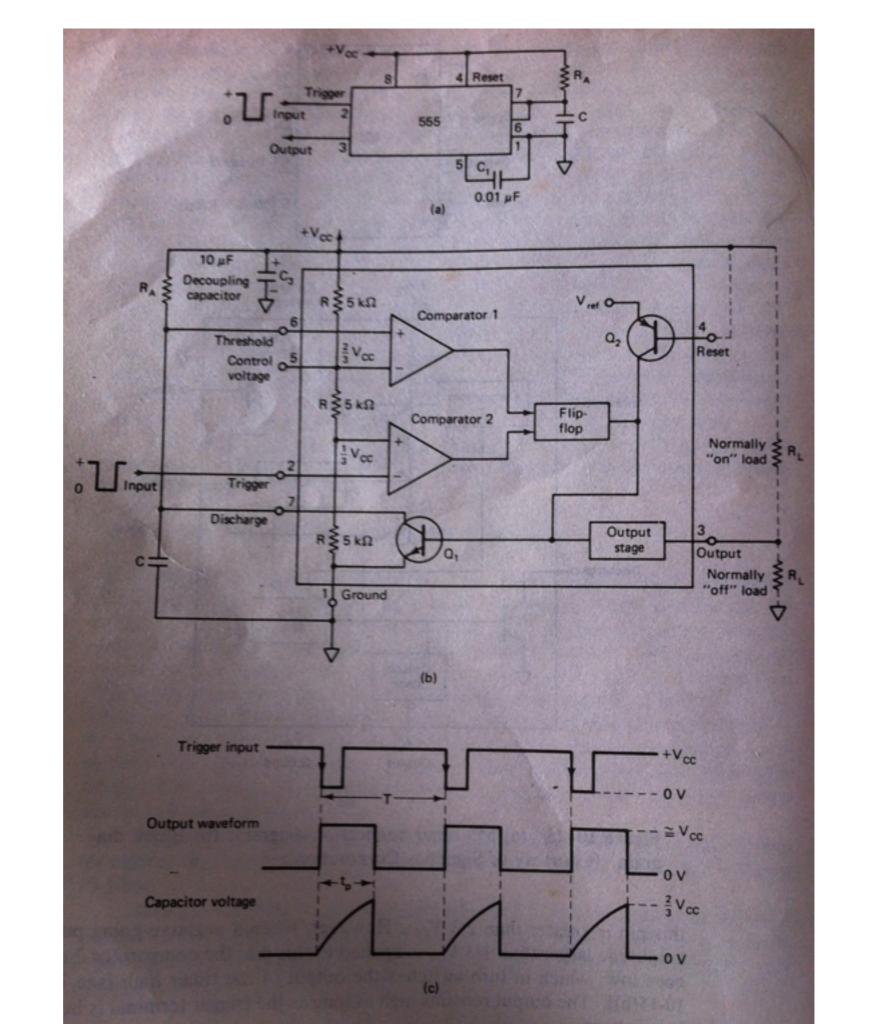

### IC555 timer internal architecture

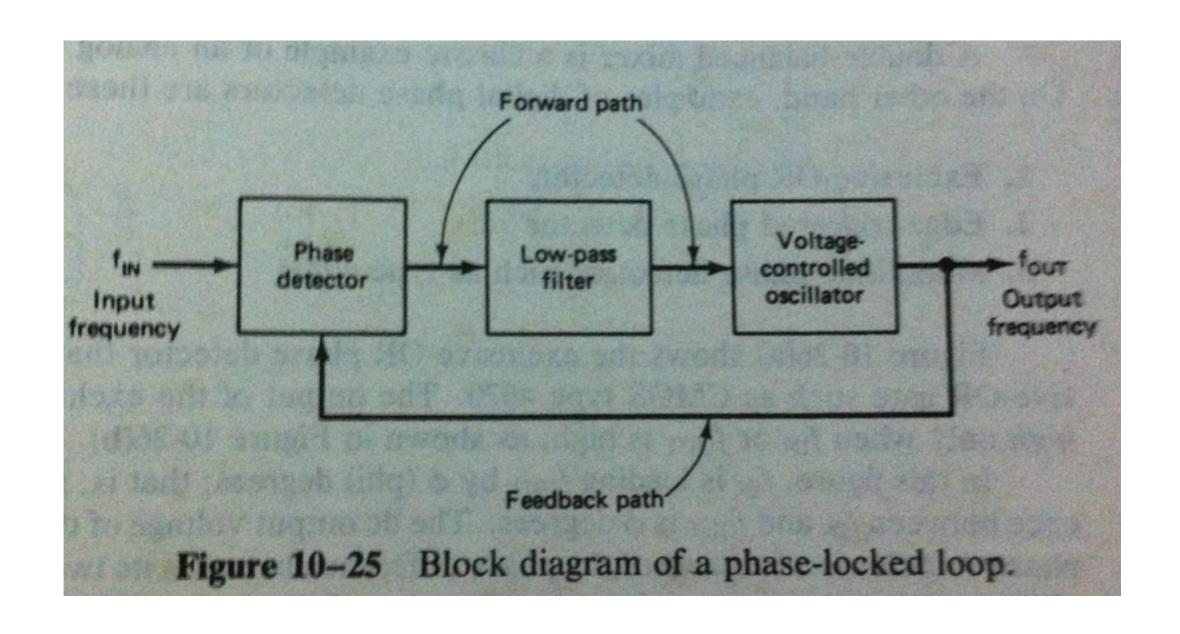

### Phase Locked Loop

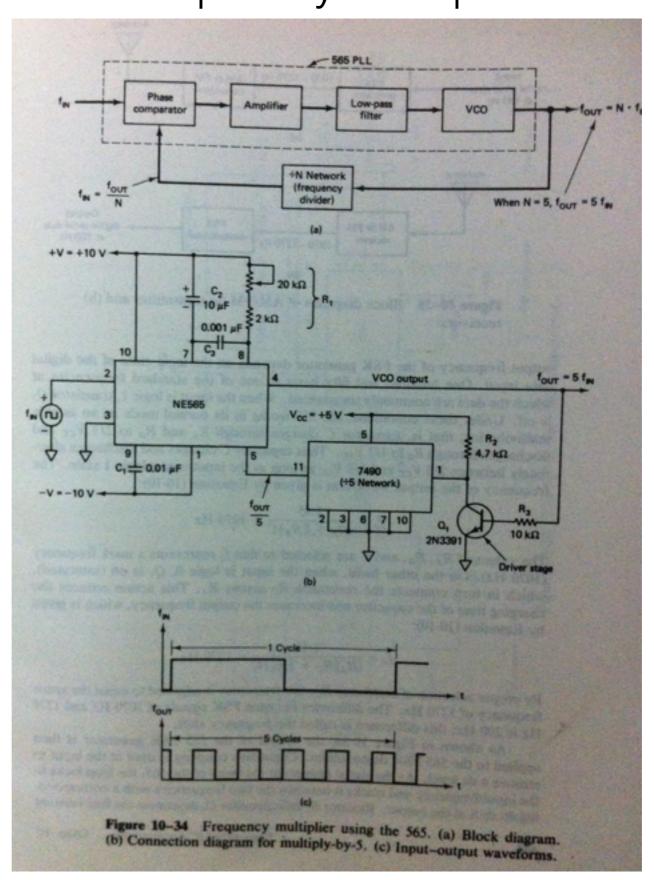

# Applications IC565 - PLL Frequency Multiplier